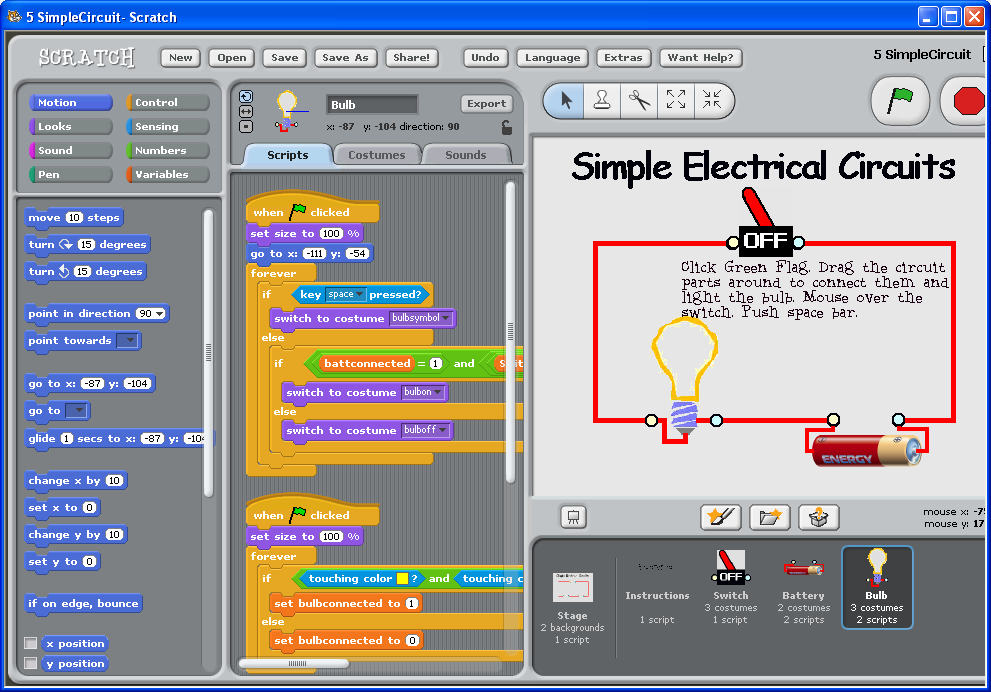

(2) Hardware is responsible for managing cache whereas, it is compilers or user's responsibility in the Scratchpad to decide which part of data or code must be employed. 1 are different : (1) Due to off-chip access and cache miss, longer latency may be experienced during cache access whereas single-cycle access latency is guaranteed by Scratchpad memory. In the following aspects scratchpad memory and cache (conventional) as display in figure. For a lesser number of processors a common scratchpad memory is an effective communication configuration.

#Interact scratchpad software#

In software-managed SPM, through implementation of software associate encryption it is probable to offer security in main memory. Main memories of multi-core processors, are susceptible to external errors like memory extraction or a bus snooping. Scratchpad memory presents together with a cache deprived of losing generality (e.g., virtualization) is capable to avoid several of the programming tasks related with general scratchpads. Scratchpad memory (SPM) in recent embedded processors is generally used to overcome the limits of cache memory. Caches are not used for data structures that organized via pointers but only use for cache-related data, such as a list then cache counterparts are managed by hardware, in terms of power and performance parameters caches are less efficient in comparison with on-chip memories controlled by the software that oftenly referred to as SPM (Scratchpad memories). To decrease the energy consumption of the memory organization, small memories (on-chip) controlled by the software are employed by various processors in embedded systems. Instead of caches use of scratchpad memories (SPMs) performs a collective role to achieve better results and cope with above mentioned major concerns.

Predictability, area, energy consumption and consistency are the major concerns in Multicore processors. Hence in order to increase the life of battery of devices, both users and manufecturers are making efforts for reducing power consumption. Certainly, become more power consuming than those machines / devices which have less features. An embedded system normally hosts a Real-Time Operating System (RTOS) as well as it is responsible for running many sophisticated applications like general media processing, network communication, and handwriting recognition. In contrast with a referenced cache-only system with just 1% performance degradation at runtime, in terms of energy consumption on average, this proposed method can achieve an 11% reduction which can be observed in experimental results.īy enhancing the processor's performance, the embedded devices, used these days, have become more advanced and powerful. By executing numerous operations on a small Real-Time Operating System the proposed Scratchpad allocation strategy is evaluated with preemptive scheduling. By profiling or static analysis, the memory accesses behaviour cannot be guessed and a RTOS (Real-Time Operating System) is mostly presented in such an environment. In multi-core processor for Scratchpad management, this proposed strategy is specifically adequate without depending on profiling information and compiler. The page table is also modified by the software so that the Scratchpad memory data block will be forwarded by the follow-up memory accesses. MRSU generated a hardware interference and the captured / identified repeatedly accessed memory block is placed, through the software, into the Scratchpad space. One of the memory addresses is considered as a captured address that is present in a repeatedly referenced memory segment. A hardware Unit MRSU (Memory Reference Sampling Unit) is introduced depend on mass-count disparity, with a very low probability that models the memory reference data stream. By using MMU an integrated (memory management unit), it can be useful for an existing embedded system that maps into a virtual space the physically addressed Scratchpad memory. An interactive and dynamic Scratchpad memory (Scratchpad) management approach is proposed in this research manuscript to target multi-core processors.

0 kommentar(er)

0 kommentar(er)